これは、ISHI会版OpenMPW TR10-2にみんなで相乗りしたxschemによる回路図とklayoutによるレイアアウト置き場です。

みんなの相乗りチップ

上記の回路図やシミュレーション、レイアウト、DRC、LVSを実行するための環境をセットアップしたWSLイメージを用意しています。

- WSL Image

- ID: ishikai

- Pass: ishikai

wsl --import-in-place ubuntu2404_TR10-2 .\ubuntu2404_TR10-2\ext4.vhdx

起動には"ubuntu2404_TR10-2.lnk"をご利用ください。

イメージも削除されるので注意してください。

wsl --unregister ubuntu2404_TR10-2

- オレンジ枠

- 初めてのInverter回路

- 緑枠

- OPAMP回路

- 紫枠

- 1bit-CPU回路

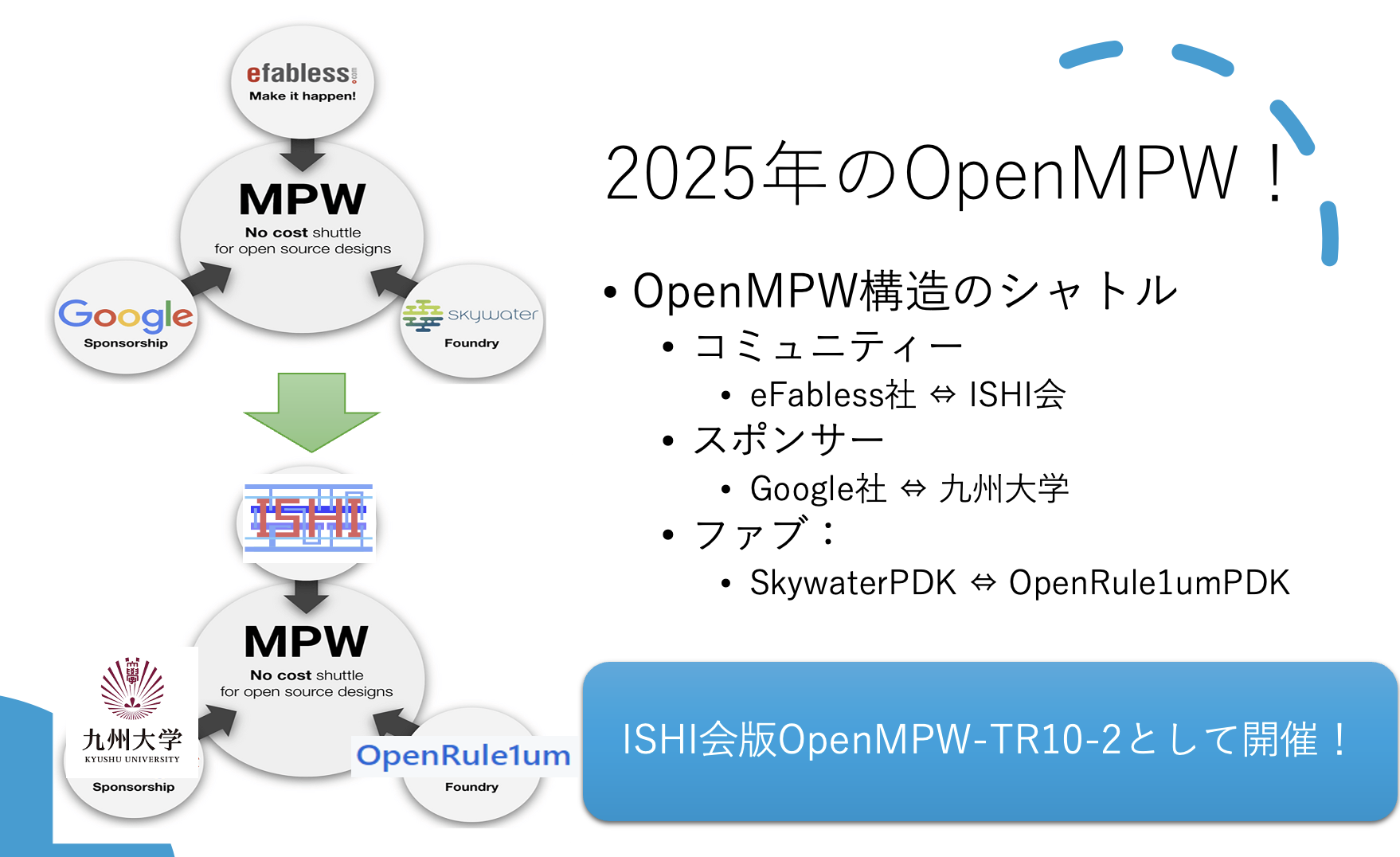

九州大学大学院システム情報科学府附属価値創造型半導体人材育成センターが主催する2025年度実習シリーズでISHI会のインバータ回路ハンズオンが採用されましたの試験運用の一環として実施されたシャトルとなります。

また、1bit-CPUハンズオンの試験運用は、九州産業大学の貞方先生の協力のもと、実施しました。

ISHI会版OpenMPW TR10-2は全16人による全18デザインの投稿がありました。

2025年09月イベント:初めての半導体設計・製造体験!一日で作るインバータ回路ハンズオンでの成果物です。

- 参加者のインバータ回路置き場

- MUX化したインバータ回路置き場

- 今回はピン数の都合で8chのマルチプレクサ/デマルチプレクサを使って実装しています。

kanoの回路

Liesegangの回路

rikulhの回路

wipesealsの回路

2025年09月イベント:二日でOPAMP回路ハンズオンでの成果物です。

インバータ回路を終えて、中級者への道の第一歩としてのハンズオンです。

arstopiaの回路

kanoの回路

ShuntaroOhnoの回路

YutakaKOTANIの回路

3zkiの回路

Rail to Rail OPAMPです。

レイアウトもかなり工夫されたものになっており、上級者になりたい方は是非参考にしてみてください。

ロジック(デジタル)回路の中級編の1bit-CPUハンズオンです。

学習内容は、「CPUやGPUのようなデジタル回路は「HDL(ハードウェア記述言語)で設計する」わけだけど、それがどうやって半導体になっているのか?を体験して理解するという内容です。

今回は、九州産業大学の貞方先生の協力のもと、試験運用を実施しました。

- 参加者の1bit-CPU回路置き場

- MUX化した1bit-CPU回路置き場

- 今回はピン数の都合で4chのマルチプレクサ/デマルチプレクサを2段で使って実装しています。

ICHIKENの回路

電気系ものづくりYouTuberのイチケンさんがレイアウトした1bit-CPUとなります。

九州産業大学の貞方先生の回路

九州産業大学の貞方先生がレイアウトした1bit-CPUとなります。

Yamada3の回路

主婦のYamada3がレイアウトした1bit-CPUとなります。

hamasunaの回路

九州大学の学生であるhamasunaがレイアウトした1bit-CPUとなります。

kanoの回路

九州大学の学生であるkanoがレイアウトした1bit-CPUとなります。

dokuniraの回路

東京大学の学生であるdokuniraがレイアウトした最小サイズクラスの1bit-CPUとなります。

ガラスマスク(レチクル)用のEBデータです。具体的には、GDSレイアウトデータを電子ビーム描画装置が読み込める独自の形式のデータに変換したものです。

-

役割

- 処理時間の短縮

- 変換処理では、半導体設計データは膨大になるため、階層構造の利用や並列処理といった技術で処理時間を短縮します。

- データ量の削減

- 微細な図形を基本図形に分解する際に、ショット数が増加したり、パターンの質が低下したりするのを防ぐために、微小ショットの発生を抑えるアルゴリズムが用いられます。

- 処理時間の短縮

- MUX含めて、無事に動作しました。

無事に動作しました。 テスト用の回路は「Open Source Silicon Magazine vol.2 ーはじめの一歩のその先へー~電気系ものづくりYouTuber イチケン氏降臨!次世代電子工作の第一歩!マイコンチップを自作しよう(アナログ編)~」の販売開始!でご案内した「Open Source Silicon Magazine vol.2」を参考にしてください。

R2R OPAMPです。秋月電子のNJM4580DD使用ヘッドホンアンプキットが駆動できました。目立ったノイズや歪みはなく、まあ普通に聞けるレベルです。

- 現状、無し。